# 特 集 フォーカス 26

フォーカス 26 〈第 2 回〉:成果事例クローズアップ(ナノプロセシング・パートナーシップ・プラットフォーム)

## 金属ナノギャップ電極の抵抗スイッチング効果

- (株) 船井電機新応用技術研究所 古田成生, 増田雄一郎

- (独) 産業技術総合研究所 ナノプロセシング・パートナーシップ・プラットフォーム

上左: (株) 船井電機 古田成生 上右:ナノプロセシング・パートナーシップ・プラットフォーム/産総研ナノプロセシング施設

## 1. はじめに

現在,低消費電力化,高速化などを目指し,様々な次世代不揮発メモリの研究が進められている。なかでも,トランジスタを用いず,2端子間の抵抗変化で情報を記録するメモリについては,半導体の微細化に対する技術的,経済的な課題に対する解決策としてのみではなく,今までに無い新しい電子デバイスを生み出せる可能性も持っているため,その行く末が注目されている。

2端子の抵抗変化素子を利用したメモリの具体例としては、トンネル磁気抵抗効果を利用した MRAM[1] を初めとして、PCMO や NiO などの遷移金属酸化物の抵抗変化を用いた ReRAM[2]、GeSbTe のような相変化材料の相変化に伴う抵抗の変化を用いた PRAM[3] などがある。また、研究段階ではあるが、スイッチ効果を持つ分子を電極間に挟んだ分子スイッチ [4]、Pt 電極と  $Ag_2S$  電極との間で Ag 原子を移動させ、電極間の接触状態を変化させる原子スイッチ [5] なども提案されている。

これら2端子の抵抗変化素子の一つとして,産総研内 藤らは,有機分子デバイスの作製中に,ナノメートル間 隔で向き合った金属電極間において,適切な電圧を印加 することで数桁のオーダーで抵抗が変化することを見出した[6]. この現象は、以下に述べるように非常に興味深い特性を示しており、ストレージデバイス等の応用が可能であると考えられるため、筆者らは現在、内藤グループと共同研究を行っている.

この素子の一番の特徴は、ナノスケールの間隔をもつ電極と、それを支える基板だけという極めてシンプルな構造である。このため、将来の応用展開において当然出てくるであろう構造に対する要求にも、対応が容易であると考えられる。また、材料の面から見ても、電極は純金属であり、作製時に MBE などの複雑な工程を必要としない。また、微細化を考えても、原子レベルでの濃度揺らぎを考えなくても済むため有利であると考えられる。一方、基板は一般的な  $SiO_2$ 上で動作している。シリコンデバイス上から  $SiO_2$  が無くなる事は考え難いので、こちらについても大きな問題となることは無いと考えている。

我々は、電子線リソグラフィ技術や集束イオンビーム 加工観察技術が蓄積されている産総研ナノプロセシング 施設において、技術相談・装置利用・チュートリアルサー ビスを利用し、金属ナノギャップ電極の微細加工および 観察評価を行った。さらには、ナノテクノロジー・ネットワーク事業におけるネットワーク機能も活用すること により、(独)物質・材料研究機構ナノテクノロジーネットワーク拠点、京都・先端ナノテクネットワークにおい て微細加工や観察・評価を効率的に進めることが出来た。 以下では、実際の研究における素子構造及び作製法、及 び代表的な結果について述べる。

\*問い合わせ:

ナノプロセシング・パートナーシップ・プラットフォーム

<del>=</del> 305-8568

茨城県つくば市梅園 1-1-1 中央第2

(独) 産業技術総合研究所 ナノ電子デバイス研究センター

電話:029-861-3210

E-mail: nppp\_info@m.aist.go.jp

## 2. 概要と基本特性

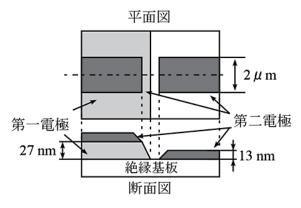

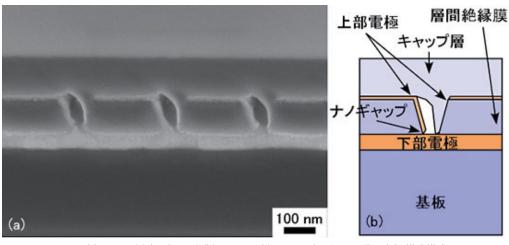

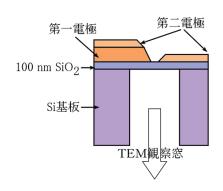

まず、本稿で述べるナノギャップスイッチの内、最も構成が簡単な二段階斜め蒸着で作製した素子の模式図を図1に示す[7].この素子は、まず、基板上に一段目となる電極を斜め蒸着で成膜、リフトオフし、その後、一段目の電極をマスクとして二段目の電極を再び斜め蒸着で成膜、リフトオフする、という二段階の工程で作られる。一段目を成膜する際に斜め蒸着を用いるのは、通常の成膜後にリフトオフを行うと、電極パターンの端が不均一になり、ギャップ幅の制御が極めて困難になっるからである。次に、ギャップ幅は一段目電極の厚さと二段目電極成膜時の蒸着角度によって決定される。詳しくは内藤らの論文に譲るが、この際の設計上のギャップ幅は13nm以上にすると、抵抗変化が起きない素子が増え、歩留まりが下がるという結果が出ている。また、後述するように、その他の構造でも問題なく動作している。

次に、電気特性について述べる。ナノギャップ素子の場合、ギャップの両側に存在する電極に電圧を印加すると、ギャップにトンネル電流が流れる。この際、重要なのは、トンネル抵抗が変化しない電圧範囲が存在することである。具体的には、1V以下の電圧であれば、1日以上印加を続けても初期の抵抗からの変化は観察されない。これは、メモリとして考えると、情報の読み出しでメモリ内容が変化しないということになり、DRAM などに比べると周辺回路にかける負担が小さいことを意味している。なお、本稿内で素子の抵抗のみを表示している場合、特に断りが無い場合は 1V以下での測定値を示している。

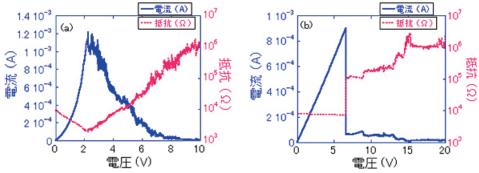

一方、ギャップの両側に存在する電極間に 3V 以上の電圧を印加した場合、電圧の高さと波形に対応してトンネル抵抗が変化する。例として、電圧を  $0V \sim 10V \sim 0V$  の順で掃引した場合の電圧—電流曲線を図 2 に示す。図中で、赤い曲線は  $0V \sim 10V$  の範囲の電流値、青い線は  $10V \sim 0V$  の範囲の電流値を示している。また、抵抗変化が明確に見えるよう、初期状態が高抵抗の素子を用いて測定を行っている。まず、赤い曲線だが、ナノギャップ素子の初期抵抗が> 1G  $\Omega$  と高抵抗であるため、2V 以

下ではほとんど電流が流れていない.が,電圧が 3V を超 えると、劇的に電流値が増加し、その後電圧が 4V から増 加するに伴い再び電流が減少する.次に、電圧を 10V か ら OV まで低下させる際の青い曲線に移る. 10V~4V ま では電圧の低下に伴い電流値が増加し、ほぼ赤い曲線と 重なっている. しかし、3V以下でも電流値の急激な低下 は見られず、結果として 1V 付近では赤い曲線と大きな差 (数値としては4~5桁程度になる)が出来ている.この時, 素子は低抵抗になっており、先ほど述べたように抵抗変 化が起きない 1V 以下の電圧で電流値を確認した場合,常 に μ A 以上の電流値が確認できる. 次に, 高抵抗状態に 戻す場合だが、5V~10V程度の電圧を印加し、高電圧 を印加した状態のままで測定を終了すれば良い. その後, 改めて 1V 以下の電圧を印加すると、電流値が nA 程度ま で減少していることが確認できる. なお, パルス駆動に ついては後述する.

その他の特性については詳しくは述べないが、現状では歩留まりの高さ、動作温度の広さ、保管の容易さといった素子の耐久性に関する部分では非常に優れていることが確認されている。また、研究初期の乱暴な駆動法でも10万回を超えるスイッチング動作を示している。このように単純な試作技術の段階で高い耐久性を示す素子は少なく、それだけにスイッチ素子として有望であると考えられる。

#### 3. 電極材料の変更

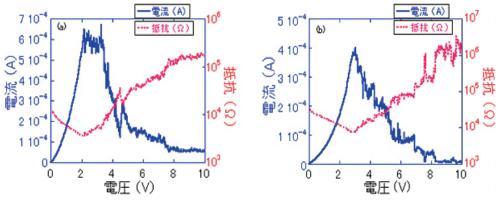

現状,かなりの種類の材料で実験を行っているが [8][9] [10],アルミのように酸化しやすい金属を除けば,殆どの材料で抵抗変化を確認している.以下に,代表的な特性として金とタンタルの電圧掃引時の電圧—電流および電圧—抵抗曲線を図3に紹介する.なお,電流は線形目盛,抵抗は対数目盛になっている.図3のうち,左が金電極に対して電圧を $0V \sim 10V$ まで掃引した際に得られた曲線,右がタンタル電極で $0V \sim 20V$ まで電圧を掃引した場合の曲線だが,一目見て差が明らかに出ている.この差が何に起因しているかは現在も研究中だが,解析例と

図1 ナノギャップ電極の模式図

図2 代表的な電気特性

図3 電圧掃引時の電圧-電流曲線,及び電圧-抵抗曲線. (a)が金,(b)がタンタル. なお,抵抗が対数目盛になっていること,(a),(b)で電圧の範囲が違うことに注意

して先の論文中での解析結果を簡単に紹介しておく. なお, この素子の興味深い所は, これだけ電気特性に差があっても, 抵抗変化の不揮発性繰り返し性などの基本的な特性が変わらないことである. このため, 電極材料の変更で特性を操作できる可能性がある. もちろん理想は1種類の電極で全ての要求を満たす事だが, 必要な特性は動作電圧から安定性まで多岐に渡るため, 特性を操作出来る可能性があるというのは重要である.

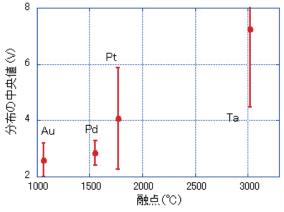

先の論文における解析では、電圧―電流曲線の内、特性を示す代表点として抵抗が極小となる部分に着目し、この部分を比較することで金属材料の変更による特性の変化を議論している. 具体的な手順としては、

- 1. 特異点や測定ごとのばらつきを押さえるため、複数の測定データから抵抗が極小になる電圧を抽出する

- 2. 電極材料ごとに集計し、抽出した電圧が正規分布に従うという仮定の下に集計結果を解析、中央値、標準偏差を求める

- 3. 中央値,標準偏差を用いて,電極材料の様々な特性との相関を見る

となる. 結果としては、抵抗率、仕事関数などとの相関は低く、図4に示すように金属の融点と高い相関を示した. これは、直ちには抵抗変化の原因が熱であるということを意味しないが、熱の影響を示唆する結果ではある.

図4 電圧分布の中央値と材料の融点との相関

### 4. 基板材料の変更

次に基板材料の変更結果である。現状までに、酸化物を中心として代表的な絶縁物を試しているが、電極とは逆に殆ど電気特性に差が見られない。また、基板材料のみでなく、基板の成膜方法を変更しても特性は殆ど影響を受けない。具体的な例として、図5にSiO基板、及びAl<sub>2</sub>O<sub>3</sub>基板上に作製した金電極の電圧一電流曲線、及び電圧一抵抗曲線を示す。一見して分かる通り、殆ど差が見られない。また、電極材料を変更した場合と同様、抵抗が極小になる電圧値の分布から中央値、標準偏差を求めたが、こちらも差は1割以下であり、誤差の範囲と考えられる程度の変化しかない。

加えて、極端な実験としては、基板材料をエッチングしてギャップ直下の酸化膜を取り去った実験があるが[11]、その場合でも大きな変化は見られなかった。これらの結果からは、ナノギャップ素子の電気特性に対する基板の与える影響はきわめて小さいと考えることが出来る。もちろん、この結果は「あらゆる絶縁材料を基板として用いることが出来る」ということを意味しないが、基板材料の選択肢が広いことを示す結果であることは間違いない。

#### 5. 側壁への素子作製

斜め蒸着による平面構造は、素子そのものが SEM などで観察できるという意味では大変優れているが、実用を考えた際には使い難い場合も多い.そのため、平面以外の構造でも試作を行っているが、今の所ほぼ全ての構造でスイッチング動作を確認している.ここでは、現実の技術に近い例として、RIE で酸化膜にホールを形成、その側壁にナノギャップを作製した例を紹介する.

大まかな作製方法としては

- 1. ウェハー表面に下部電極となる金属薄膜を作製

- 2. 下部電極上に絶縁膜を作製

- 3. 絶縁膜にコンタクトホールを形成. 原理的にはホールの直径は問わないが, 今回は上部電極の斜め蒸着を容易にするために直径を100nm程度として設計, 作製

図 5 (a) が SiO 基板, (b) が  $Al_2O_3$  基板上の金電極での電圧ー電流曲線,及び電圧ー抵抗曲線. これらの形状に多少の差はあるが、トポグラフ的には変化は見られない.

#### 4. ホール側壁に上部電極を作製

となる. ナノギャップについては,4番の工程で上部電極を成膜する際に斜め蒸着を用い,ホール自体の影により側壁の一部のみに電極が成膜することで作製している. 角度を適切に設定してやることで,下部電極直上にナノギャップを作製することが可能になる.この時,ホールの露光にはNIMS. 京大のEB 描画装置を用いた.

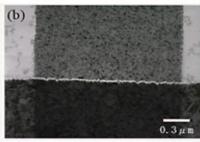

また、構造観察用にホールを複数作製した素子に対し、NPFのFIBを用いて断面を作製した。実際の写真を図6の(a)、構造の模式図を図6の(b)に示している。FIBによる断面作製時の保護、断面観察時の上部電極とW保護膜との分離、素子の保護及び封止に向けた研究の一環などの様々な理由から、上部電極上にさらに絶縁膜を成膜している。空隙があることからも分かる通り、最表面の絶縁膜についても斜めに成膜している。なお、図6の構造自体は断面確認用に設計しているので電気特性を測定することは出来ないが、同様のプロセスを用いて作製した素子では平面上に作製した金ナノギャップ電極と変わらない電気特性を記録している。この状態でスイッチング現象が起きることからも、この現象自体は非常に微細な領域で起きる現象であることが確認できる.

#### 6. スイッチングの高速性

本研究テーマにおいては、当然だが構造だけでは無く、 駆動法に関する研究も行っている。このうち、以下では パルス入力による高速駆動の可能性と、その派生として 抵抗状態の多値化について解説する。

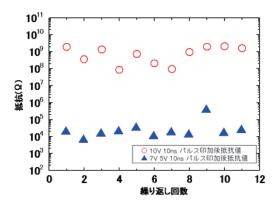

ナノギャップ素子の実用化を考えた場合、殆どの用途ではスイッチングに必要な時間は短いほうが良く、数十秒かけて電圧を掃引している時間はない。厳密に言えばパルスと言っても電圧が連続的に変化するのだが、ここでは電圧波形の入力全体に必要な時間を問題にしている。そこで、我々はパルス入力による高速駆動についても検討しており、良好な結果を得ている。実際、

- 1. 素子に  $10\text{ns} \sim 100~\mu~\text{s}$  のパルスを入力する 2. その後、1V 以下の電圧で抵抗値を読み出す という単純な実験でも十分抵抗変化が起きることが確認 出来ている.

- また、単に抵抗が変化するだけで無く、実際にスイッチング動作も確認できている.以下では、最も高速な例として、10nsで抵抗スイッチングを起こした例について解説する.駆動法としては、入力パルスの幅を10nsに固

図6 (a) ホール側壁に素子を作製し、FIBで断面を切り出した SEM像、(b) 構造模式図

図 7 ナノギャップスイッチに 10ns 幅パルスを入力した際の 抵抗変化

定し、電圧レベルを変化させて素子に入力、その後、1V付近の電圧において抵抗値を確認する、という手順である。その結果、低抵抗状態の素子に10Vの電圧のパルスを入力すると高抵抗に移行し、高抵抗状態の素子に7Vと5Vの連続した電圧のパルスを入力すると低抵抗状態に移行することが確認できた。この抵抗値の変化を複数回繰り返し、抵抗値を読み出したプロットが図7になる。10nsという短いパルス幅にもかかわらずナノギャップの抵抗値が変化し、入力した電圧値に対応した抵抗値をと

ることが分かる. 更に高抵抗域, 低抵抗域の分離もよく 出来ており, スイッチング素子として動作していること が確認できる.

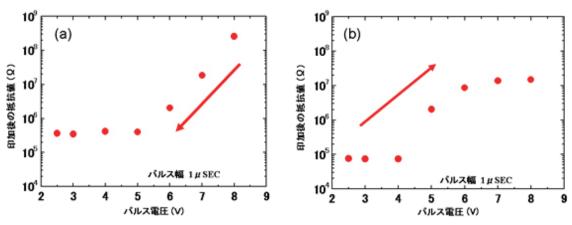

## 7. ナノギャップの抵抗値の多値化[12]

図7の高速動作実験では、スイッチング動作として極力抵抗値の変化が大きくなる様、入力電圧も10Vと5Vというように大きく変化させている。これに対して、パルス電圧を連続的に変化させた場合の抵抗値の推移を示したのが図8である。(a) は高抵抗状態の素子に対して、入力するパルス電圧を8Vから1Vずつ降下させた場合、(b) は逆に、低抵抗状態の素子に対して入力電圧を2Vから1Vずつ上昇させた場合である。(a)、(b) どちらの場合でも、パルス電圧の変化に対応して抵抗値が順に変化していることが分かる。現状では素子の抵抗値は入力前の状態の影響を受けており、6V入力後の抵抗が(a)と(b)で異なるなどの問題があるが、入力電圧の設定次第では中間の抵抗値を取りうるという事実は確認できる。

次に、中間値を取りうるという事実を積極的に利用するため、素子の抵抗値を複数の領域に分離することを検

図8 入力パルスの電圧を徐々に変化させた場合の抵抗値の推移 (a) 電圧降下時,(b) 電圧上昇時

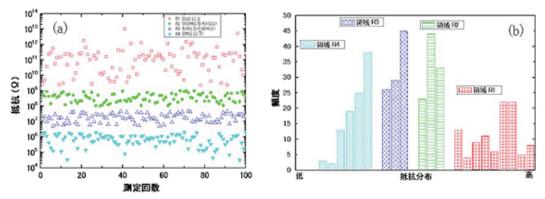

図9 (a) 4段階の電圧パルスを入力した際の抵抗変化, (b) 測定された抵抗値の分布

討した. 現状では,入力するパルス電圧を12V,10V,8V,5V に設定する事に加え,意図した領域から外れた抵抗値を取った場合には書き直しを行うことによっておおまかに4つの領域に分離することが出来ている.この結果を図9に示す.(a)が実際に測定された抵抗値,(b)が測定された抵抗値の分布である.ただ,この実験で用いた駆動法は未完成であり,抵抗値分布の先鋭化,書き直し回数の減少などを実現するために改良を進めている.

#### 8. 動作原理の解明

ここまで構造,電気特性について紹介してきたが,もちろん動作原理の解明に向けた研究も行っている.代表例としてはガス雰囲気の変更による特性変化の観察[13]などがあるが,これは産総研が中心になって進めているので,詳しくは参考文献を参照されたい.以下では,原理解明の一環として行っている TEM による構造観察について簡単に触れる.

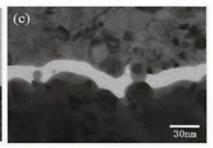

現在、ナノギャップ素子の抵抗変化の原因はギャップ両側、もしくは片側の電極が変形し、トンネル電流が流れているギャップ幅が変化することによって起きていると推測されている。が、この変化は  $1 \sim 2$ nm と予想されており、SEM での観察は解像度的に厳しい。また、ギャップのアスペクト比が高いため、AFM でも完全には観察できていない。そこで、現在、図 10 に示すように NIMS のSi 深堀エッチング装置で基板を削り、スイッチング動作可能な状態で TEM 観察可能な素子を作製、TEM での観察を行っている。実際に観察された TEM 像を図 11 に示す。

図 10 TEM 観察用素子の模式図

しかし、図のように構造自体の観察には成功しているが、 抵抗変化の原因究明まではいたっていない.

## 9. おわりに

ここまでナノギャップ素子の現状を紹介してきたが、 基礎研究の出口に近づきつつあると考えている。今後は、 より量産に適した構造、抵抗値を高い精度で制御できる 駆動法などの開発を目指していく。

#### 謝辞

本報告内の仕事の一部は、文部科学省の「ナノテクノロジー・ネットワーク」プロジェクトの支援を受けて、(独)産業技術総合研究所ナノプロセシング施設、(独)物質・材料研究機構ナノテクノロジー拠点、京都・先端ナノテクネットワーク内で実施されました。また、本研究はNEDO「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発ナノギャップ不揮発性メモリ技術の研究開発」より助成を受けています。

## 参考文献

[1] Y. Choi, H. Tsunemotsu, S. Yamagata, H. Okuyama, Y. Nagamine, and K. Tsunekawa: Jpn. J. Appl. Phys. 48 (2009) 120214.

[2] A. Sawa: Oyo Butsuri 75 (2006) 1109.

[3] M. Terao, T. Morikawa, and T. Ohta: Jpn. J. Appl. Phys. 48 (2009) 080001.

[4] J. L. He, B. Chen, A. K. Flatt, J. J. Stephenson, and C. D. Doyle: Nature Materials 5 (2006) 63.

[5] K. Terabe, T. Hasegawa, T. Nakayama, and M. Aono: Hyomen Kagaku 27 (2006) 232.

[6] Y. Naitoh, M. Horikawa, H. Abe, and T. Shimizu: Nanotechnology 17 (2006) 5669.

[7] Y. Naitoh, K. Tsukagoshi, K. Murata, and W. Mizutani: e-J. Surf. Sci. Nanotechnology 14 (2003) 41.

[8] Y. Naitoh, Y. Morita, M. Horikawa, H. Suga, and T. Shimizu: Appl. Phys. Express 1 (2008) 103001.

図 11 TEM による平面ナノギャップ素子の観察結果

- [9] S. Furuta, T. Takahashi, Y. Naitho, M. Horikawa, T. Shimizu, and M. Ono: Jpn. J. Appl. Phys. 47 (2008) 1806.

[10] Y. Naitoh, K. Yanagi, H. Suga, M. Horikawa, T. Tanaka, H. Kataura, and T. Shimizu: Appl. Phys. Express 2 (2009) 035008.

- [11] Y. Naitoh, M. Horikawa, and T. Shimizu: Jpn. J. Appl.

- Phys. 47 (2008) 400.

- [12] Y. Masuda, T. Takahashi, S. Furuta, M. Ono, T. Shimizu, and Y. Naitoh: Appl. Surf. Sci. 256 (2009) 1028.[13] Y. Naitoh, M. Horikawa, and T. Shimizu: Jpn. J. Appl. Phys. 49 (2010) 01AH08